好了,進入正是,說說lvds調試。如下圖,采用軟硬結合板設計,左側為FPGA主板部分,右側主要是一些接口,包括Camlink、VGA,中間采用柔性電路板相連。

按照連載3的程序調試lvds接口,使用bank5的差分管腳輸出lvds信號,結果采集卡采不到圖,這下壞了,開始懷疑引腳分配不正確,一番檢查,問題不在這;

接著覺得走線可能不對,看了看PCB,5對差分信號,對內線長差控制在0.254mm內,對間線長差控制在2mm內,走線沒有問題;

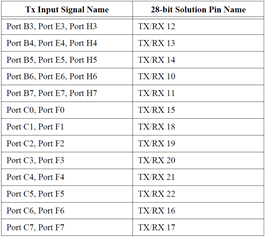

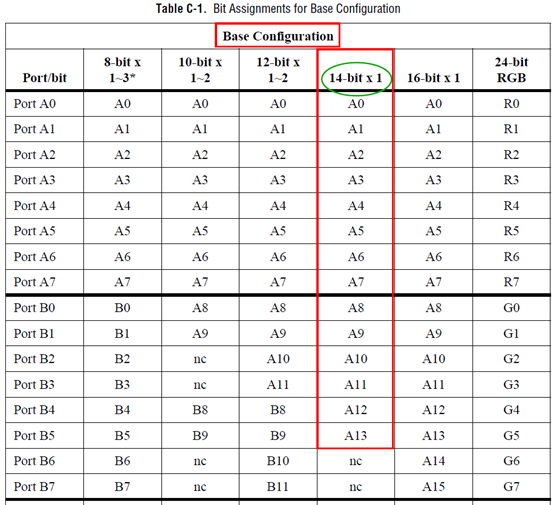

再懷疑Camlink位分配不正確,Camlink在base模式下包含11對差分線(4對數據,1對時鐘,2對串口,4對相機控制),Camlink協議中有詳細的位分配表,

下表說明了在base模式下,各種圖像模式(24bit RGB、8bit、10bit、14bit、16bit灰度等)下位分配情況。

查看287手冊,就可得到位分配信息。

又是一番檢查,位分配完全正確。

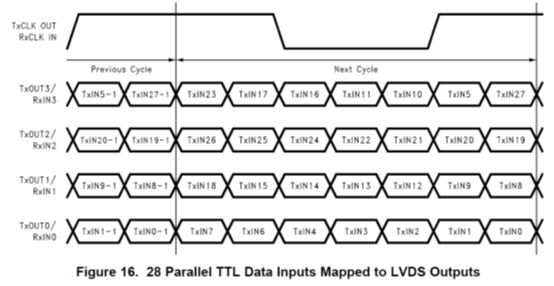

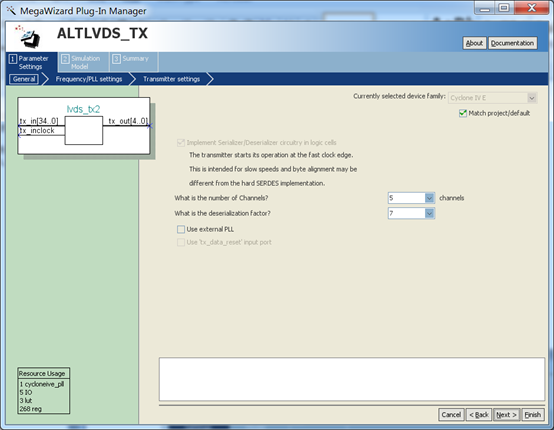

datain3 datain2 datain1 datain0 經過同學的點撥,發現了問題,原來在于時鐘的串行化問題,我使用的是lvds_tx核的tx_outclock作為差分時鐘,而287的手冊上7倍時鐘串化對應的時鐘信號分別為1,1,0,0,0,1,1,問題已經比較明白了,clk差分通道數據如下,使用5個channels,如下圖所示。

cl_clk

重新編譯,下載,圖像輸出正常,lvds調試完成!!

由于lvds_tx核使用了一個ip核,邏輯中使用一個,qsys中使用一個,這樣總共4個ip核就用了3個,相關使用外用pll,結果出來的數據又不對了,至今沒有解決這個問題,后面有進展了再行吧。